Knowledge Base Help Center

Quartus II Variable과 Signal의 차이

VHDL의 변수와 신호는 매우 유사합니다. 둘 다 할당 된 모든 유형의 데이터를 보유하는 데 사용할 수 있습니다. 가장 분명한 차이점은 변수는 : = 할당 기호를 사용하는 반면 신호는 <= 할당 기호를 사용한다는 것 입니다. 그러나 차이점은 이것보다 더 중요하며 언제 어떤 것을 사용해야하는지 명확하게 이해해야합니다.

신호 대 변수 :

- 변수는 프로세스 내부에서만 사용할 수 있으며 신호는 프로세스 내부 또는 외부에서 사용할 수 있습니다.

- 한 프로세스에서 생성 된 변수는 다른 프로세스에서 사용할 수 없으며 신호는 단일 프로세스에서만 할당 될 수 있지만 여러 프로세스에서 사용할 수 있습니다 .

- 변수는 키워드 처리 후 키워드 begin 전에 정의해야 합니다 . 신호는 begin 문 앞에 아키텍처에서 정의됩니다 .

- 변수는 : = 할당 기호를 사용하여 할당됩니다. 신호는 <= 할당 기호를 사용하여 할당됩니다.

- 할당 된 변수는 즉시 할당 값을 갖습니다. 신호는 신호가 할당 값을 취하는시기를 알기 위해 조합 또는 순차 코드인지에 따라 다릅니다.

이해해야 할 가장 중요한 사항 (그리고 가장 큰 혼란의 원인)은 변수가 할당 값을 즉시 가져 오는 반면 신호는 신호가 조합 또는 순차 코드로 사용되는지에 따라 달라진다는 것 입니다. 조합 코드에서 신호는 즉시 할당 값을 취합니다. 순차 코드에서 신호는 본질적으로 할당 값을 즉시 사용하지 않는 플립 플롭을 생성하는 데 사용됩니다. 그들은 한 클럭 사이클을 사용합니다. 일반적으로 초보자는 변수 사용을 피하는 것이 좋습니다. 그들은 많은 혼란을 야기 할 수 있으며 종종 도구로 합성하기가 어렵습니다.

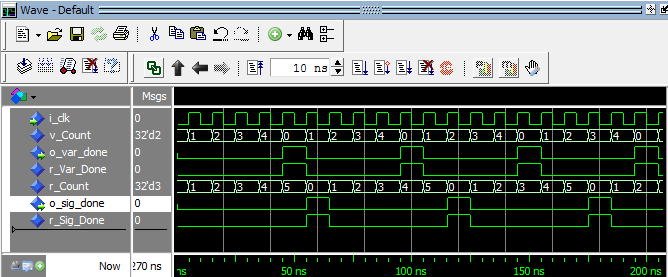

아래 예는 신호가 변수와 다르게 작동하는 방식을 보여줍니다. 공지 사항 r_Count 및 v_Count는 것을 표시 동일하게,하지만 실제로는 매우 다르게 동작합니다.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity variable_vs_signal is

port (

i_clk : in std_logic;

o_var_done : out std_logic;

o_sig_done : out std_logic

);

end variable_vs_signal;

architecture rtl of variable_vs_signal is

signal r_Var_Done : std_logic := '0';

signal r_Count : natural range 0 to 6 := 0;

signal r_Sig_Done : std_logic := '0';

begin

VAR_VS_SIG : process (i_clk)

variable v_Count : natural range 0 to 5 := 0;

begin

if rising_edge(i_clk) then

v_Count := v_Count + 1; -- Variable

r_Count <= r_Count + 1; -- Signal

-- Variable Checking

if v_Count = 5 then

r_Var_Done <= '1';

v_Count := 0;

else

r_Var_Done <= '0';

end if;

-- Signal Checking

if r_Count = 5 then

r_Sig_Done <= '1';

r_Count <= 0;

else

r_Sig_Done <= '0';

end if;

end if;

end process VAR_VS_SIG;

o_var_done <= r_Var_Done;

o_sig_done <= r_Sig_Done;

end rtl;Testbench:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity variable_vs_signal_tb is

end variable_vs_signal_tb;

architecture behave of variable_vs_signal_tb is

constant c_CLK_PERIOD : time := 10 ns;

signal r_Clock : std_logic := '0';

signal w_Var_Done : std_logic;

signal w_Sig_Done : std_logic;

component variable_vs_signal is

port (

i_clk : in std_logic;

o_var_done : out std_logic;

o_sig_done : out std_logic

);

end component variable_vs_signal;

begin

r_Clock <= not r_Clock after c_CLK_PERIOD/2;

variable_vs_signal_inst : variable_vs_signal

port map (

i_clk => r_Clock,

o_var_done => w_Var_Done,

o_sig_done => w_Sig_Done

);

end behave;

변수 대 신호 테스트 벤치 파형

변수는 시뮬레이션에 표시하기가 약간 까다로울 수 있습니다. Modelsim을 사용하는 경우 Modelsim의 파형 창에서 변수를 보는 방법에 대해 자세히 읽어보십시오 . 위의 파형을주의 깊게보십시오. o_var_done이 5 번째 클럭 사이클마다 펄스를 보내는 방법을 보십니까? 그러나 o_sig_done이 6 번째 클럭 사이클마다 펄스를 보내는 방법을 아십니까? 신호와 변수를 사용하여 데이터를 저장하면 매우 다른 동작이 생성됩니다 . 코드가 생성 할 내용을 명확하게 이해하고 코드를 시뮬레이션하여 원하는대로 작동하는지 확인하십시오!